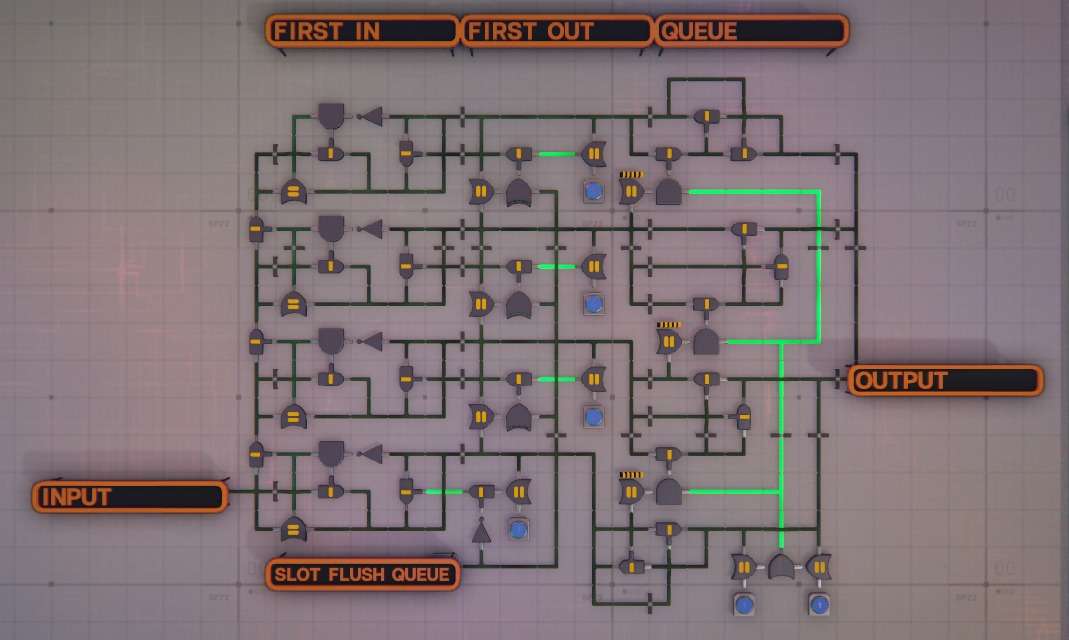

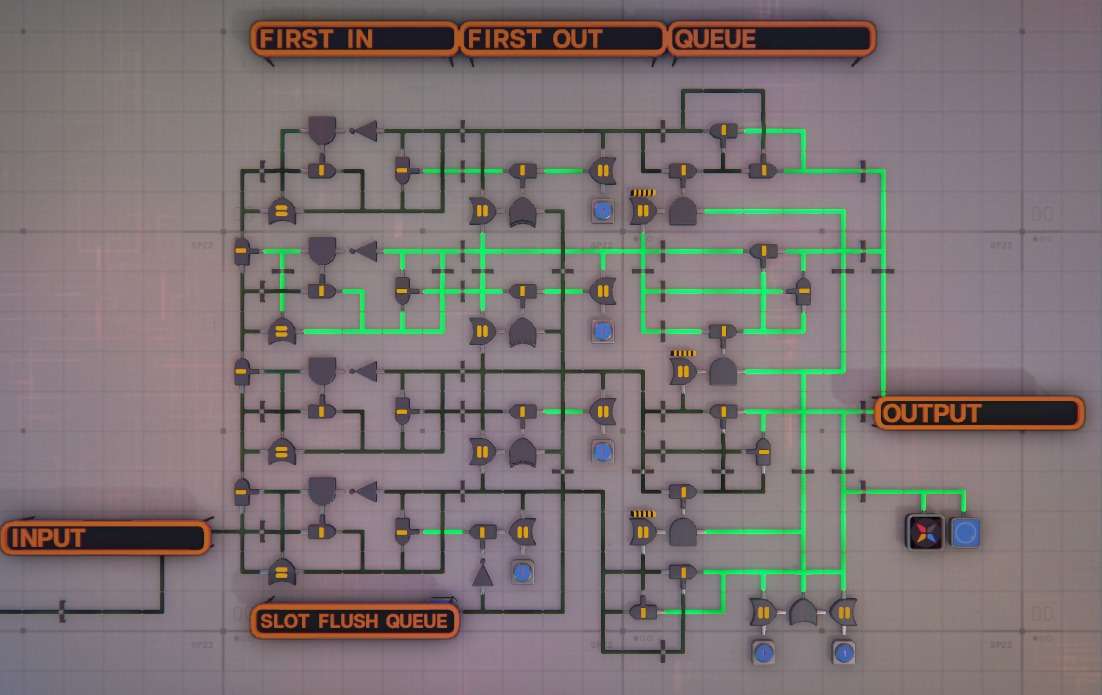

Reliable FIFO Queue

By Cabboose.

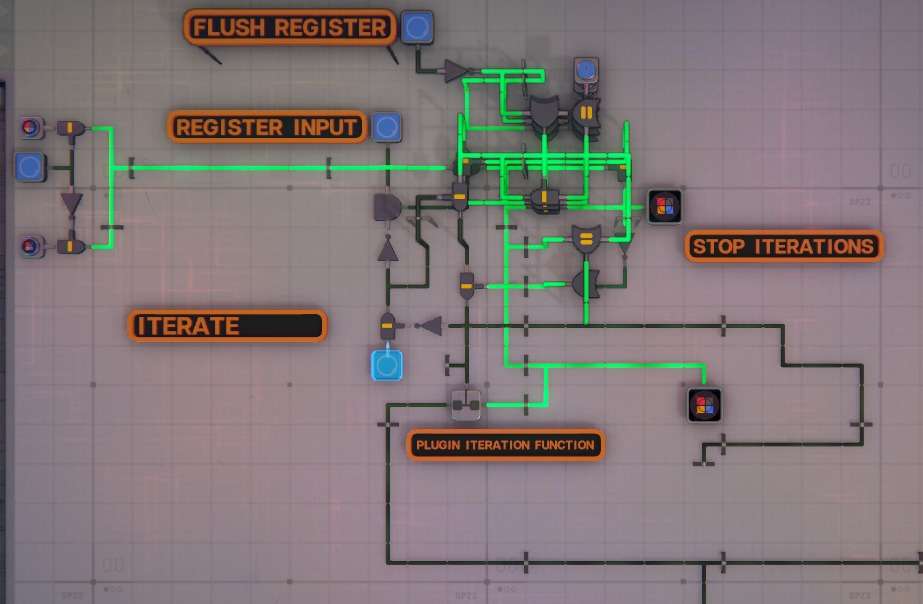

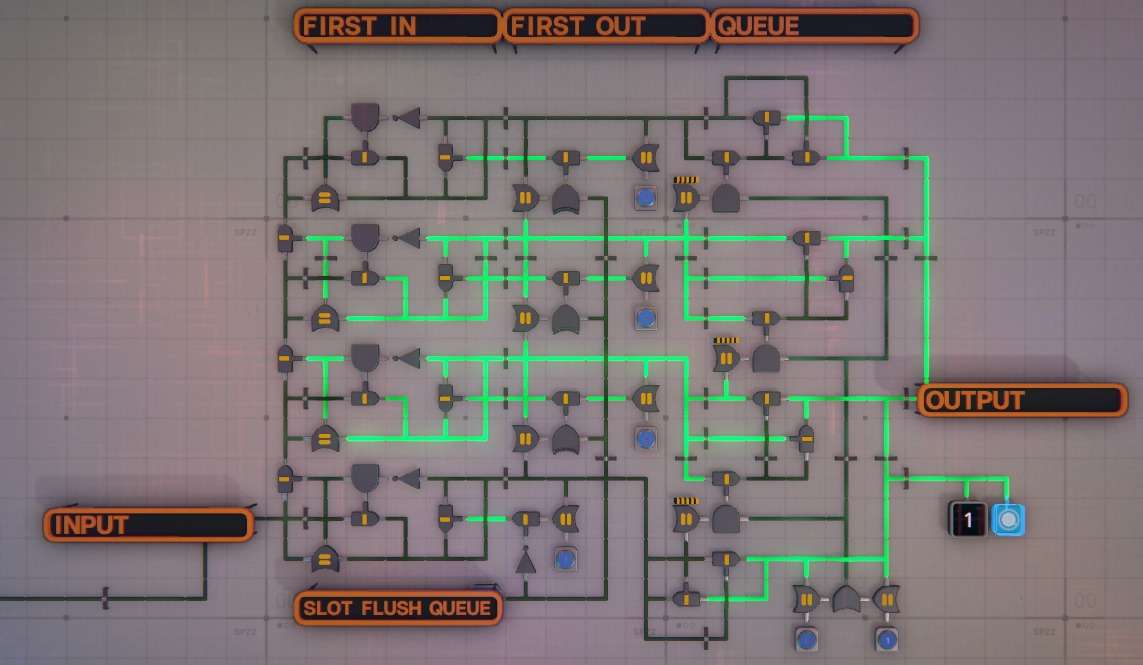

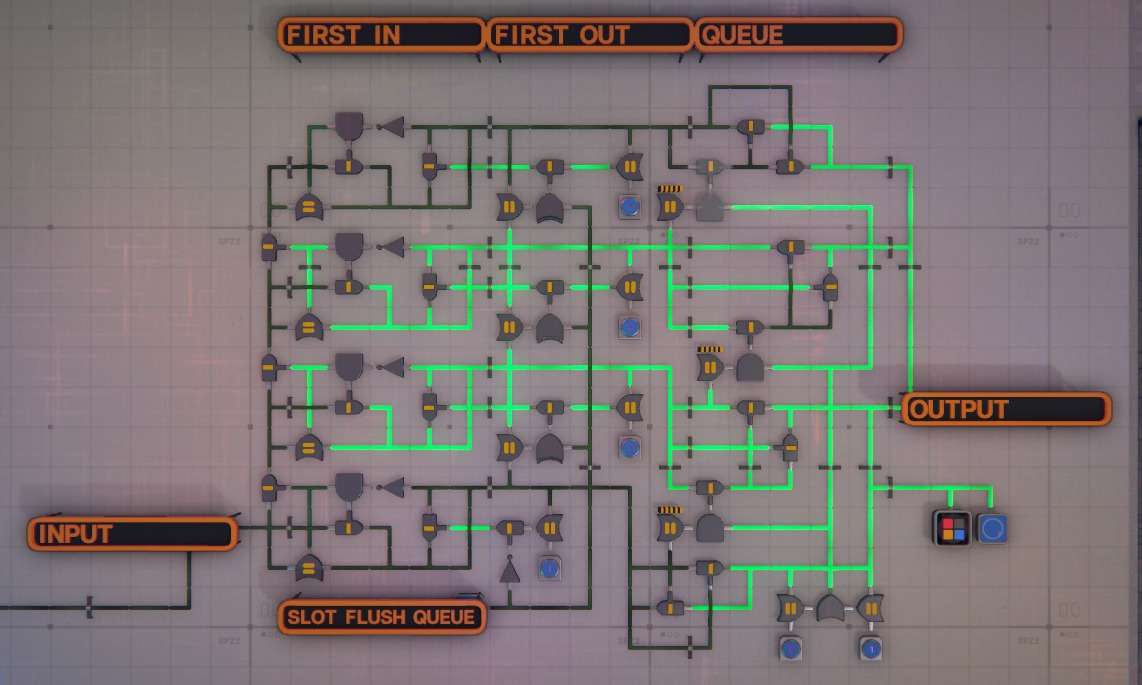

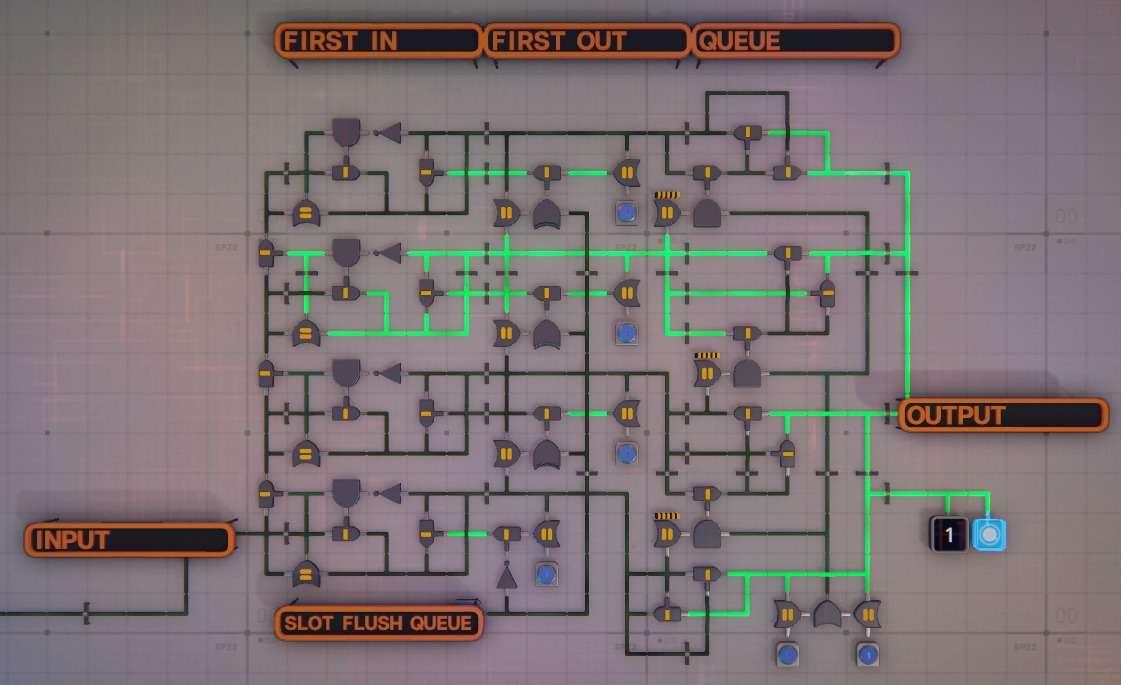

Made a FIFO Queue which works very reliably (given sufficient signals to register events; I have a 3 cell buffer iterator which always registers all events with the queue).

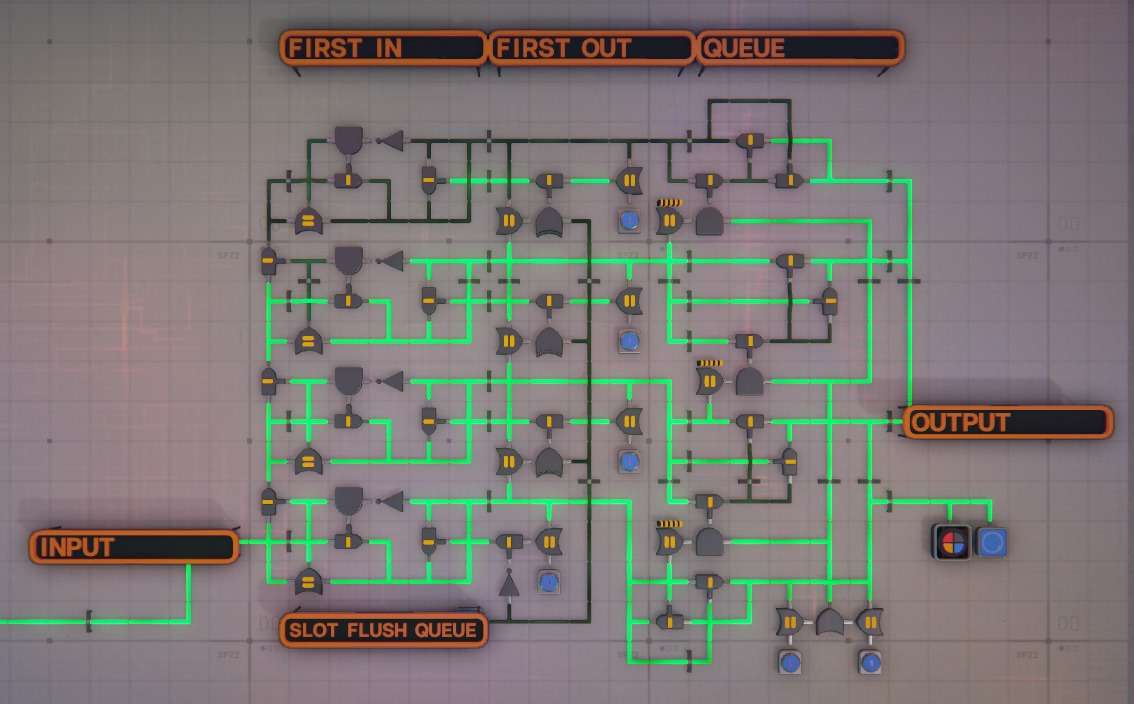

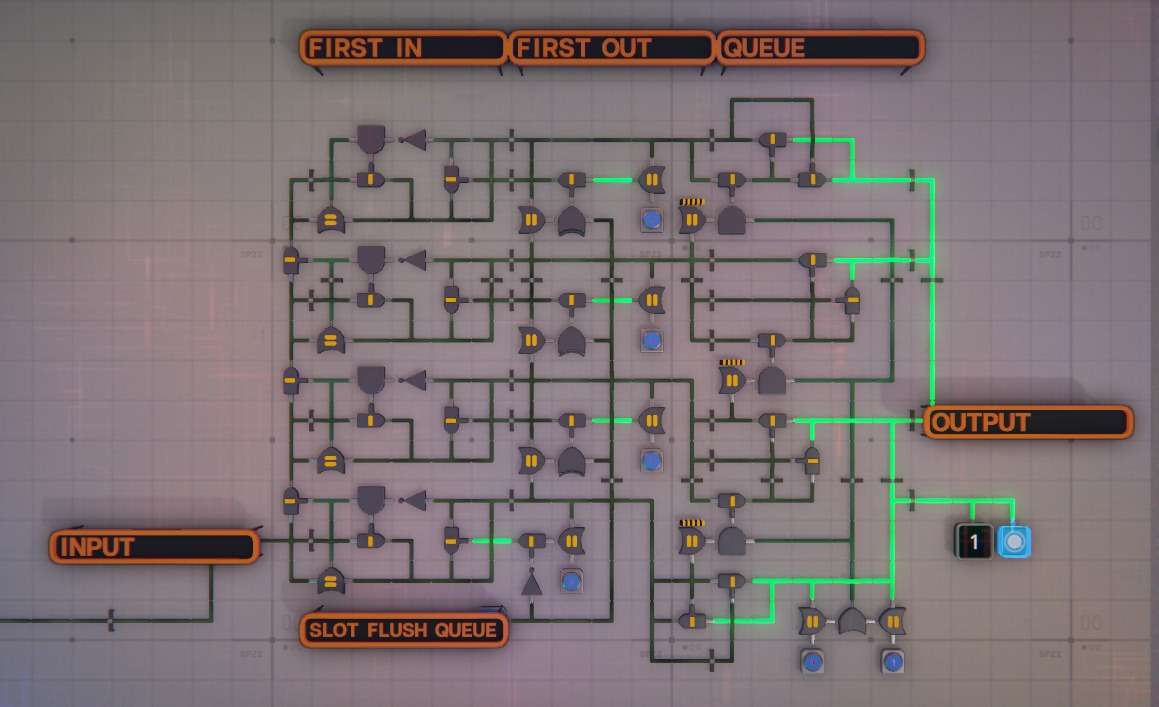

The fun part is that there is only one output. When you’re done with a signal, just send a ‘1’ signal back into it (you’ll have to account for transmission between platforms with receiver/transmitter pair) and it’ll cause a conflict which will ‘consume’ the signal. once you’re ready to receive the next one (listen to the output for a ‘1’ signal), remove your ‘1’ signal and you’ll receive the next signal.

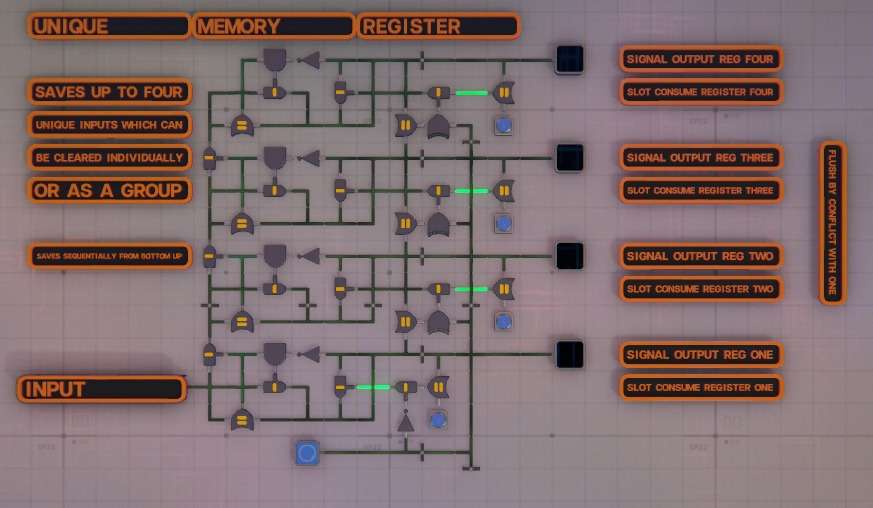

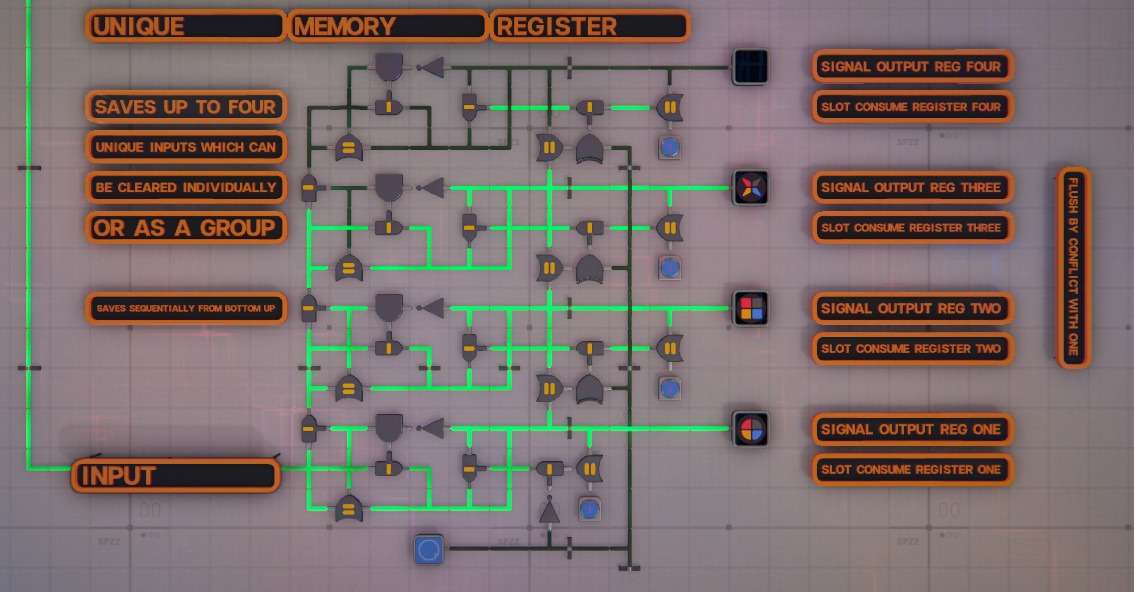

The FIFO is a unique memory register with extra bits and bobs. There’s a lot of fiddly checks and redundancy to make sure it works reliably.

An example can be seen where I use the iterator to prepare 3 layers in the FIFO and then consume them one by one.

- Google Drive (2 Kb).

Click to enlarge…

I sincerely hope this was helpful. Good luck to you!

Be the first to comment